Min-Young Lee

Lmo970901@hanyang.ac.kr

Education

- 21.03 ~ Present : Integrated Ph.D. Course in Electronic Engineering, Hanyang University, Korea

- 17.03 ~ 21.02 : B.E. in System Semiconductor Engineering, Sangmyung University, Korea

Research Interests

- Hardware Accelerator (RTL Design)

- Deep Learning for Vision, Language

- ASIC Design & Implementation (MPW)

Computer Skills

- Hardware Description Languages - Verilog, System Verilog

- Synopsys Tools

- Design Compiler (Synthesis)

- IC Compiler II (Place & Route)

- Formality (Formal Verification)

- VCS (Logic Simulator)

- PrimeTime (STA)

- PrimePower (Power Analysis)

- Cadence Tool - Virtuoso (Layout)

- Siemens Tool - Calibre (DRC & LVS)

- Mentor Tool - Modelsim (Logic Simulator)

- FPGA Tools - Xilinx Vivado, Intel(Altera) Quartus

MPW Projects

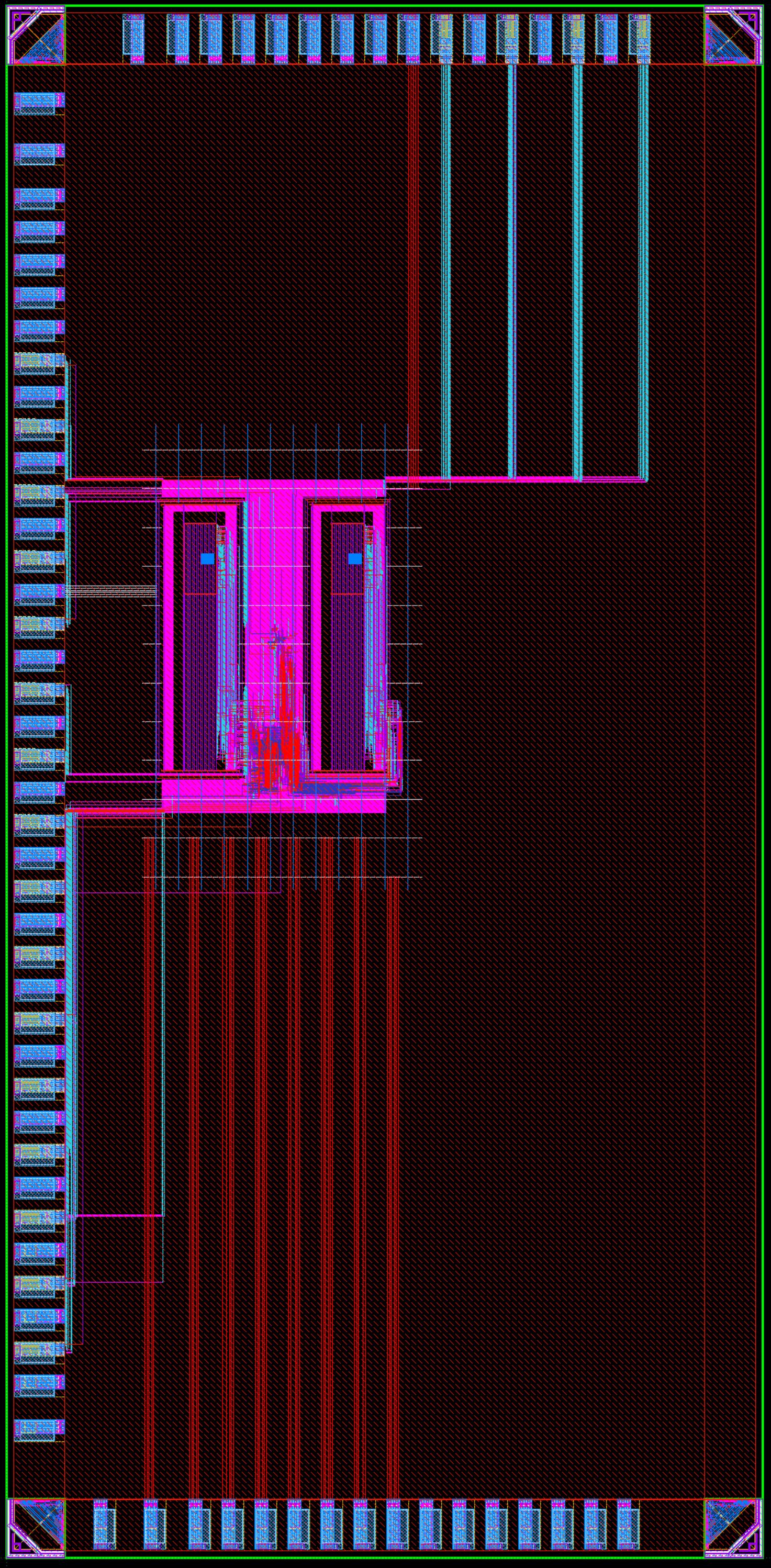

- LR-SoC: A Lightweight RISC-V SoC - Samsung 28nm LPP CMOS Process (2022.07)

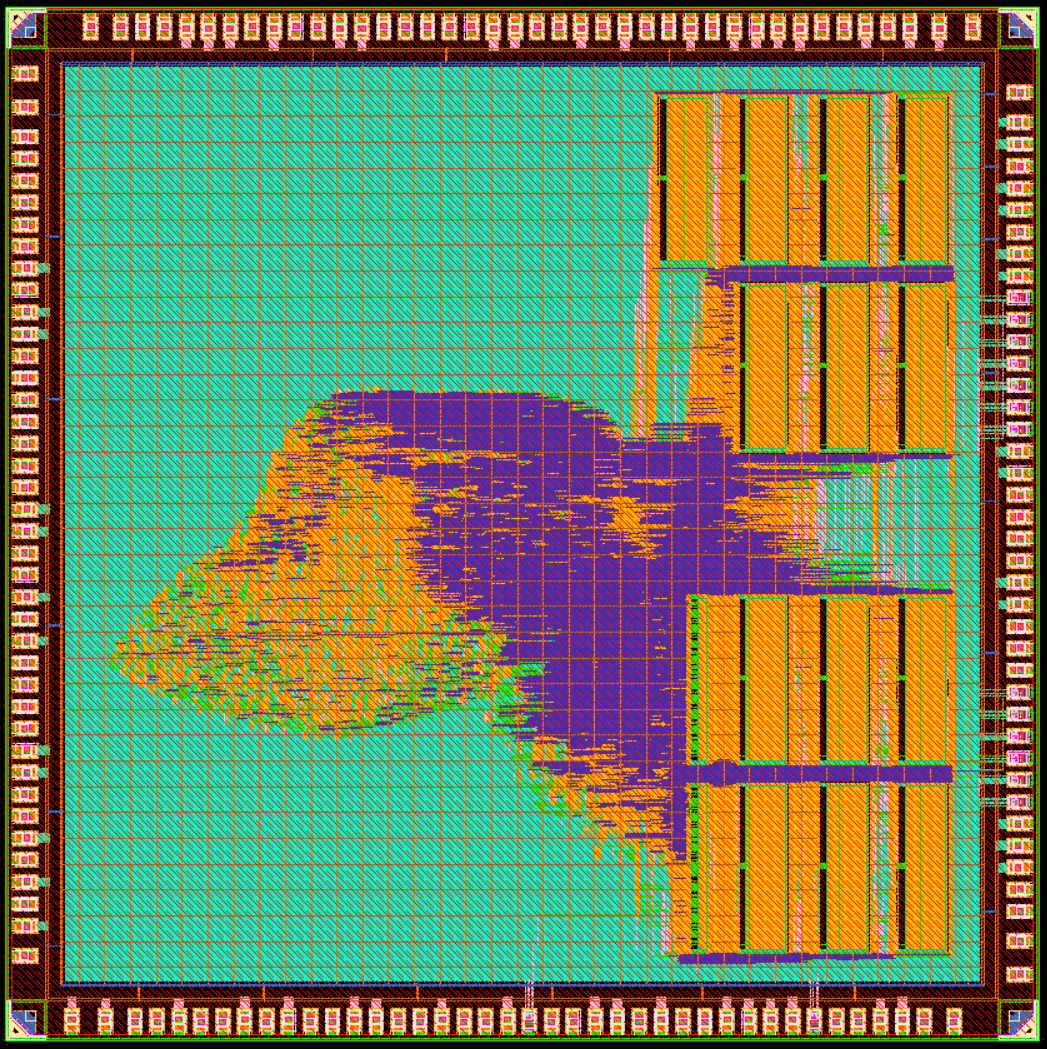

- Efficient Transformer Encoder on RISC-V SoC - Samsung 28nm FD-SOI CMOS Process (2026.03)

Others

- 24.03 ~ : National Military Service (Active Service, Technical Research Personnel)